# P25C512H

# 512-Kbit Serial SPI bus EEPROM

Datasheet Rev.1.2

# **General Description**

The P25C512H is Serial Peripheral Interface (SPI) compatible EEPROM (Electrically Erasable Programmable Memory) device. It contains a memory array of 512 Kbits (64 Kbytes), which is organized in 128 bytes per page.

### **Features**

- Single supply voltage: 1.7 V to 5.5 V

- Max clock frequency:

- ♦ 15 MHz clock from 4.5 V to 5.5 V

- ♦ 5 MHz clock from 1.7 V to 5.5 V

- Serial Peripheral Interface (SPI) Compatible

- → Standard SPI: C, S#, D, Q, W#, HOLD#

- ♦ Mode 0 and Mode 3

- Memory array

- ♦ 512 Kbits of EEPROM

- ♦ Page size: 128 bytes

- Write

- ♦ Byte/Page Write within 5ms

- Additional Write lockable page (Identification Page)

- Additional 128 bits Serial Number (Unique ID)

- Hardware Controlled Locking of Protected Sectors by WP Pin

- Transparent ECC on each group of four bytes which can correct 1 bit error

- High Reliability

♦ Endurance: 4 Million Write Cycles

♦ Data Retention: 200 Years♦ HBM: 6 kV

■ Package: PDIP8,SOP8 (150mil/208mil),TSSOP8,MSOP8,DFN8,UDFN8

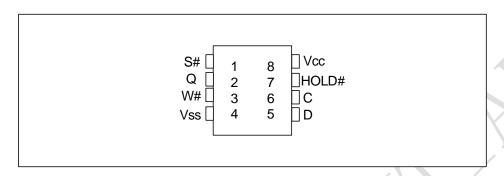

# 1. Pin Configuration

## 1.1 Pin Configuration

PDIP8/SOP8 (150mil/208mil)/TSSOP8/MSOP8/DFN8/UDFN8

#### 1.2 Pin Definition

Table 1-1 Pin Definition for PDIP8/SOP8 (150mil/208mil)/TSSOP8/MSOP8/DFN8/UDFN8 Packages

| Pin | Name  | Туре   | Description        |

|-----|-------|--------|--------------------|

| 1   | S#    | Input  | Chip Select        |

| 2   | Q     | Output | Serial Data Output |

| 3   | W#    | Input  | Write Protect      |

| 4   | Vss   | Ground | Ground             |

| 5   | D     | Input  | Serial Data Input  |

| 6   | С     | Input  | Serial Clock       |

| 7   | HOLD# | Input  | Hold               |

| 8   | Vcc   | Power  | Power Supply       |

# 1.3 Signal Description

During all operations, VCC must keep stable and within the specified valid range: VCC (min) to VCC (max). All the input and output signals must keep high or low according to voltages of VIH, VOH, VIL or VOL, as specified in: DC and AC parameters. These signals are described next.

## 1.3.1 Serial Data Output (Q)

This output signal is used to transmit data sequentially into the device. Data is shifted out on the falling edge of Serial Clock (C).

## 1.3.2 Serial Data Input (D)

This output signal is used to transmit data sequentially into the device. It receives instructions, addresses, and the data to be recorded. Values are latched on the rising edge of Serial Clock (C).

### 1.3.3 Serial Clock (C)

This input signal provides the serial interface timing. The instructions, addresses, or data present in the Serial Data Input (D) are glued on the rising edge of Serial Clock (C). The data on the Serial Data Output (Q) changes at the lower edge of Serial Clock (C).

#### 1.3.4 Chip Select (S#)

During the signal is high, the device is deselected and Serial Data Output (Q) is at high impedance. The device will be in the Standby Power mode, only when an internal Write cycle is in progress. Driving Chip Select (S#) low selects the device, placing it in the Active Power mode.

After power-up, a falling edge on Chip Select (S#) is required before beginning instruction.

#### 1.3.5 Hold (HOLD#)

The Hold (HOLD#) signal is used to pause any serial communications with the device without deselecting the device.

During the Hold condition, the Serial Data Output (Q) is high impedance, and Serial Data Input (D) and Serial Clock (C) are Don't Care.

To start the Hold condition, you must select the device, with driven low of Chip Select (S#).

#### 1.3.6 Write Protect (W#)

The main purpose of this input signal is to freeze the size of the area of memory that is protected against Write instructions (as specified by the values in the BP1 and BP0 bits of the Status Register).

This pin must be driven either high or low, and must be stable during all Write instructions.

# 1.3.7 VCC supply voltage

Vcc is the supply voltage

#### 1.3.8 VSS ground

Vss is the benchmark for all signals, including voltage supply Vcc.

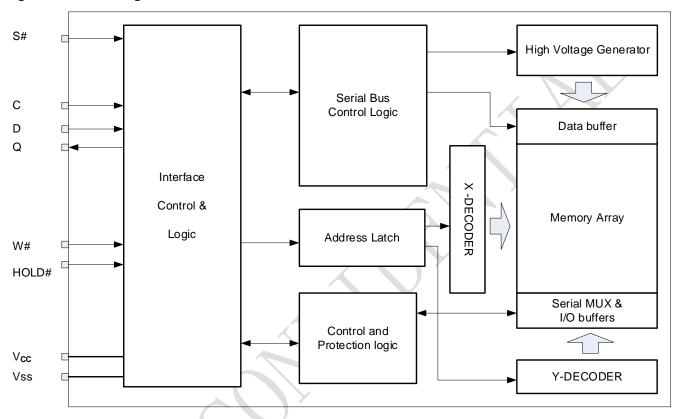

# 2. Block Diagram

The memory is organized as shown in the following figure

Figure 2-1 Block Diagram

# 3. Connecting to the SPI bus

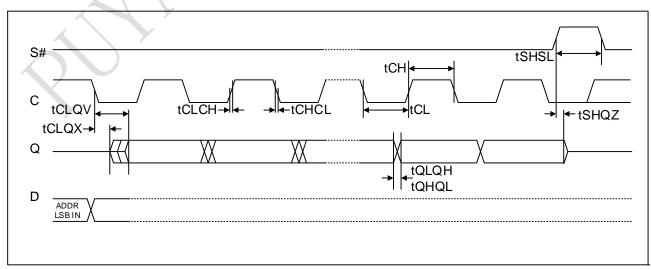

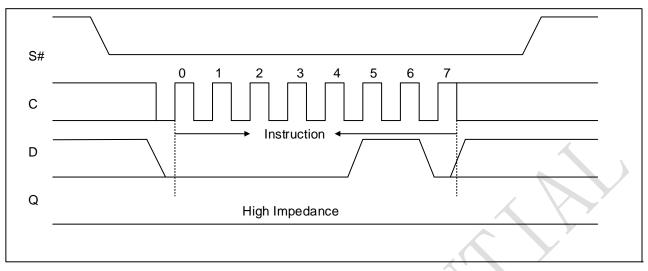

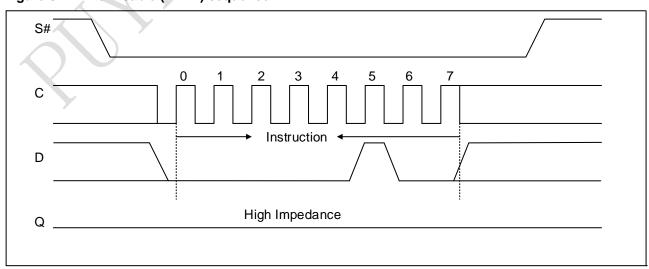

All instructions, addresses and input data bytes are shifted in to the device, most significant bit first. The Serial Data Input (D) is sampled on the first rising edge of the Serial Clock (C) after Chip Select (S#) goes low.

All output data bytes are shifted out of the device, most significant bit first. The Serial Data Output (Q) is latched on the first falling edge of the Serial Clock (C) after the instruction (such as the Read from Memory Array and Read Status Register instructions) have been clocked into the device.

Vss Vcc R D Q С CIQI D D Q Master R SPI SPI R Memory Memory Device Device CS0 CS1 S# W# HOLD# S# W# HOLD#

Figure 3-1 The master and memory devices on the SPI bus

Note:

1. The Write Protect (W#) and Hold (HOLD#) signals should be driven, high or low as appropriate.

Figure 3-1 shows an example of two memory devices connected to an SPI bus master. Only one memory device is selected, so only one memory device drives the Serial Data Output (Q) line at a time. The other memory devices are high impedance.

The pull-up resistor R (represented in Figure 3-1) ensures that a device is not selected if the Master leaves the S line in the high impedance state.

In applications where the Master keeps all SPI bus lines simultaneously high impedance (for example, if the Master is reset during an instruction transmission), the clock line (C) must be connected to an external pull-down a resistor that ensures the C line is pulled low (While S# line is pulled high) when all inputs / outputs are high impedance: this ensures that S and C do not go high at the same time and tSHCH Is guaranteed to meet the requirements. The typical value for R is  $100k\Omega$ .

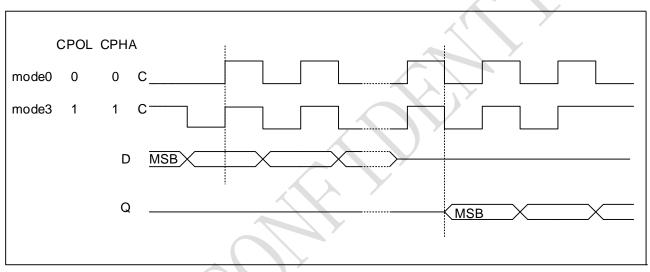

#### 3.1 SPI Modes

When incorrect command is inputted to this device, this device becomes standby mode and keeps the standby

mode until next S# falling edge. In standby mode, Q pin of this device should be High-Z. When correct command is inputted to this device, this device becomes active mode and keeps the active mode until next S# rising edge.

Input data is latched on the rising edge of Serial Clock (C) and data shifts out on the falling edge of Clock (C). The difference of serial peripheral interface mode 0 and mode 3 is shown as Figure 3-2:

For these two modes, input data is latched in on the rising edge of Serial Clock (C), and output data is available from the falling edge of Serial Clock (C).

- CPOL = 0, CPHA = 0

- CPOL = 1, CPHA = 1

Figure 3-2 SPI modes supported

#### Note:

CPOL indicates clock polarity of serial master, CPOL=1 for SCLK high while idle, CPOL=0 for SCLK low while not transmitting. CPHA indicates clock phase. The combination of CPOL bit and CPHA bit decides which serial mode is supported.

# 4. Electrical Characteristics

Table 4-1 Absolute Maximum Ratings [1]

| Symbol           | Parameter                     | Min. | Max. | Units |

|------------------|-------------------------------|------|------|-------|

| T <sub>STG</sub> | Storage Temperature           | -65  | 150  | °C    |

| T <sub>A</sub>   | Ambient operating temperature | -40  | 125  | °C    |

| Vcc              | Supply Voltage                | -0.5 | 6.5  | V     |

| $V_{10}$         | Input or output range         | -0.5 | 6.5  | V     |

| l <sub>oL</sub>  | DC output current             | -    | 5    | mA    |

Note: [1] Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

**Table 4-2 Pin Capacitance**

| Symbol          | Parameter                      | Max. | Units | Test Condition [1]    |

|-----------------|--------------------------------|------|-------|-----------------------|

| Соит            | Output capacitance (Q)         | 8    | pF    | Vоит = 0 V            |

|                 | Input capacitance (D)          | 6    | pF    | V <sub>IN</sub> = 0 V |

| C <sub>IN</sub> | Input capacitance (other pins) | 6    | pF    | V <sub>IN</sub> = 0 V |

Note: [1]. Sampled only, not 100% tested, at  $T_A = 25$  °C and a frequency of 5 MHz

Table 4-3 DC Characteristics (Unless otherwise specified, VCC = 1.7V to 5.5V, TA = -40°C to 125°C)

| Symbol                          | Parameter              | Min.   | Тур.   | Max.    | Unit | Test Condition                                                                             |

|---------------------------------|------------------------|--------|--------|---------|------|--------------------------------------------------------------------------------------------|

| Vcc                             | Supply Voltage         | 1.7    | -      | 5.5     | V    |                                                                                            |

| Isb                             | Standby Current        | -      | 0.5[2] | 8.0     | μΑ   | Vcc =5.5V, Vin = Vss or Vcc<br>Ta=85°C                                                     |

| 150                             | Standby Current        | )-     | 10.0   | 20.0    | μΑ   | Vcc =5.5V, Vin = Vss or Vcc<br>Ta=125°C                                                    |

| 1 [1]                           | Supply Current/road)   | -      | 0.6    | 2.0     | mA   | V <sub>CC</sub> = 2.5 V, Q=open,<br>C = 0.1 V <sub>CC</sub> / 0.9 V <sub>CC</sub> at 5 MHz |

| lcc <sub>1</sub> <sup>[1]</sup> | Supply Current(read)   |        | 1.0    | 3.0     | mA   | $V_{CC}$ = 5.5 V, Q=open,<br>C = 0.1 $V_{CC}$ / 0.9 $V_{CC}$ at 5 MHz                      |

| Icc2 <sup>[1]</sup>             | Supply Current(write)  | -      | 2.5    | 6.0     | mA   | During twr, Vcc = 2.5 V                                                                    |

| lu                              | Input Leakage Current  | -      | -      | ±2.0    | μΑ   | V <sub>IN</sub> = V <sub>CC</sub> or Vss                                                   |

| ILO                             | Output Leakage Current | -      | -      | ±2.0    | μΑ   | V <sub>OUT</sub> = V <sub>CC</sub> or Vss                                                  |

| VIL                             | Input Low Level        | -0.45  | -      | 0.3Vcc  | V    | 1.7 V ≤ Vcc ≤5.5V                                                                          |

| VIH                             | Input High Level       | 0.7Vcc | -      | Vcc+0.5 | V    | 1.7 V ≤ Vcc ≤5.5V                                                                          |

| VoL                             | Output Low Level       | -      | -      | 0.3     | V    | $I_{OL} = 0.15 \text{ mA}, V_{CC} = 1.8 \text{ V}$                                         |

| VoH                             | Output high voltage    | 0.8Vcc | -      | -       |      | $I_{OH} = -0.1 \text{ mA}, VCC = 1.7 \text{ V}$                                            |

Note: [1] Characterized values, not tested in production

[2] Typ. ISB @ VCC =5.5V,  $T_{\text{A}}$  =25  $^{\circ}\text{C}$

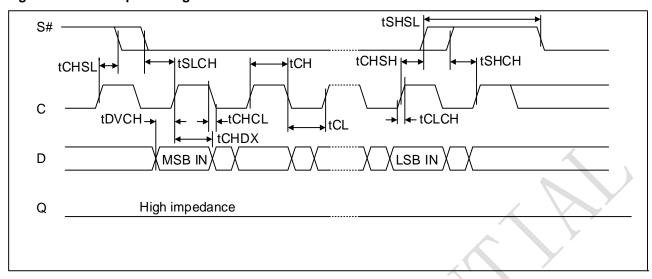

**Table 4-4 AC Characteristics** (Unless otherwise specified, VCC = 1.7V to 5.5V, TA =  $-40^{\circ}$ C to 125°C, CL=30pF, Test Conditions are listed in Notes [2]

| Symbol            | Parameter                                  | 1.7  | 7≤V <sub>CC</sub> ≤ | 5.5           | 4.5  | 5.5  | Units |     |

|-------------------|--------------------------------------------|------|---------------------|---------------|------|------|-------|-----|

|                   |                                            | Min. | Тур.                | Max.          | Min. | Тур. | Max.  |     |

| fc                | Clock frequency                            | DC   | -                   | 5             | DC   | -    | 15    | MHz |

| t <sub>SLCH</sub> | S active setup time                        | 60   | -                   | -             | 15   | -    | -     | ns  |

| tshch             | S not active setup time                    | 60   | -                   | -             | 15   | -    | -     | ns  |

| tsHSL             | S deselect time                            | 90   | -                   | -             | 30   | -    | ,-    | ns  |

| tchsh             | S active hold time                         | 60   | -                   | -             | 15   | -    |       | ns  |

| tchsL             | S not active hold time                     | 60   | -                   | -             | 15   | -    | -     | ns  |

| tсн               | Clock high time                            | 80   | -                   | -             | 20   | -    | -     | ns  |

| t <sub>CL</sub>   | Clock low time                             | 80   | -                   | -             | 20   | -    | -     | ns  |

| tclch             | Clock rise time                            | -    | -                   | 2             | -    | -    | 2     | us  |

| t <sub>CHCL</sub> | Clock fall time                            | -    | -                   | 2             | 1    | -    | 2     | us  |

| t <sub>DVCH</sub> | Data in setup time                         | 20   | -                   | 1             | 5    | -    | -     | ns  |

| tcHDX             | Data in hold time                          | 20   | -                   |               | 10   | -    | -     | ns  |

| tннсн             | Clock low hold time after HOLD# not active | 60   |                     | <b>A</b> -, ) | 15   | -    | -     | ns  |

| thLch             | Clock low hold time after HOLD# active     | 60   | -                   | -             | 15   | -    | -     | ns  |

| t <sub>CLHL</sub> | Clock low set-up time before HOLD# active  | 0    | -                   | -             | 0    | -    | -     | ns  |

| t <sub>CLHH</sub> | Clock low set-up time before HOLD# not     | 0    |                     | -             | 0    | -    | -     | ns  |

| tsнqz             | Output disable time                        | -    | <i>-</i>            | 80            | -    | -    | 20    | ns  |

| t <sub>CLQV</sub> | Clock low to output valid                  | -    | -                   | 80            | 1    | -    | 20    | ns  |

| t <sub>CLQX</sub> | Output hold time                           | 0    | -                   | -             | 0    | -    | -     | ns  |

| tqlqh             | Output rise time                           | ı    | -                   | 80            | ı    | -    | 20    | ns  |

| tQHQL             | Output fall time                           | •    | -                   | 80            | ı    | -    | 20    | ns  |

| thhav             | HOLD# high to output valid                 | ı    | -                   | 80            | ı    | -    | 20    | ns  |

| t <sub>HLQZ</sub> | HOLD# low to output high-Z                 | -    | -                   | 80            | 1    | -    | 20    | ns  |

| t <sub>W</sub>    | Write time                                 | -    | -                   | 5             | -    | -    | 5     | ms  |

#### Notes:

Table 4-5 Reliability Characteristic [1]

| Symbol             | Parameter      | Test condition                        | Min.      | Unit          |

|--------------------|----------------|---------------------------------------|-----------|---------------|

| EDR <sup>[2]</sup> | Endurance      | TA ≤ 25 °C, VCC(min) < VCC < VCC(max) | 4,000,000 | Write cycles  |

| EDK                | Endurance      | TA = 85°C, VCC(min) < VCC < VCC(max)  | 1,000,000 | vviite cycles |

| DRET               | Data retention | TA = 55 °C                            | 200       | Years         |

| DKET               | Data retention | TA = 85 °C                            | 50        | i eals        |

#### Note:

<sup>[1]</sup> tCH + tCL must never be lower than the shortest possible clock period, 1/fC(max).

<sup>[2]</sup> Characterized only, not tested in production.

<sup>[1]</sup> The Write cycle endurance is defined for groups of four data bytes located at addresses [4\*N, 4\*N+1, 4\*N+2, 4\*N+3] where N is an integer, or for the status register byte. This parameter is ensured by characterization and is not 100% tested [2] Under the condition:3.3V, Page mode

Figure 4-1 Serial input timing

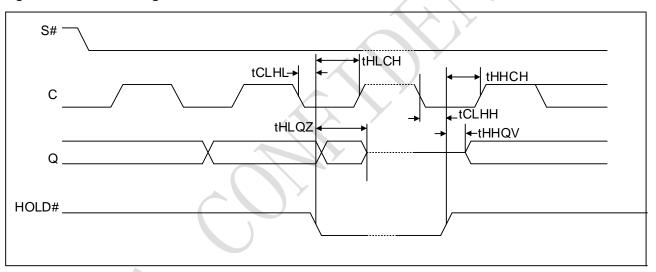

Figure 4-2 HOLD# timing

Figure 4-3 Serial output timing

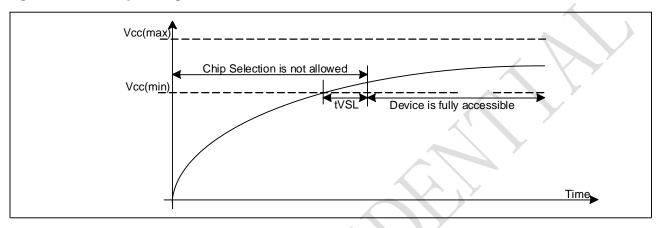

#### **Device Power-Up**

The EEPROM has a built-in power-on-reset circuit that initializes itself at the same time during power-on.

Unsuccessful initialization may cause a malfunction. To operate the power-on-reset circuit normally, the following conditions must be satisfied to raise the power supply voltage.

When initialization is successfully completed by the power-on-reset circuit, the EEPROM enters the standby status. tVSL is the time required to initialize the EEPROM. No instructions are accepted during this time.

Figure 4-4 Power up Timing

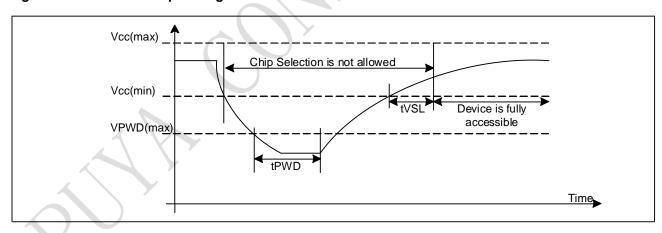

#### Power Up/Down and Voltage Drop

For Power-down to Power-up operation, the  $V_{\text{CC}}$  of EEPROM device must below VPWD for at least tPWD timing. Please check the table below for more detail.

Figure 4-5 Power down-up Timing

| Symbol | Parameter                                                                           | min | max    | unit |

|--------|-------------------------------------------------------------------------------------|-----|--------|------|

| VPWD   | V <sub>CC</sub> voltage needed to below VPWD for ensuring initialization will occur |     | 0.7    | V    |

| tPWD   | The minimum duration for ensuring initialization will                               | 300 |        | us   |

|        | occur                                                                               |     |        |      |

| tVSL   | V <sub>CC</sub> (min.) to device operation                                          | 100 |        | us   |

| tVR    | V <sub>cc</sub> Rise Time                                                           | 1   | 500000 | us/V |

# 5. Operating features

# 5.1 Supply voltage (VCC)

#### 5.1.1 Operating supply voltage (V<sub>CC</sub>)

Before selecting memory and issuing a command, an effective and stable  $V_{cc}$  voltage must be applied within the specified range [ $V_{cc}$ (min),  $V_{cc}$ (max)] (see operating conditions in DC and AC parameters). This voltage must remain stable and valid until the end of the instruction transfer and for a write instruction until the end of the internal write cycle (tW). To ensure a stable DC supply voltage, it is recommended to disconnect the  $V_{cc}$  line with a suitable capacitor (usually between 10 and 100 nF) near the  $V_{cc}$ / Vss device pins.

#### 5.1.2 Device reset

In order to prevent erroneous instruction decoding and inadvertent Write operations during power-up, a power-on-reset (POR) circuit is included. At power-up, the device does not respond to any instruction until  $V_{CC}$  reaches the POR threshold voltage. This threshold is lower than the minimum  $V_{CC}$  operating voltage.

At power-up, when Vcc passes over the POR threshold, the device is reset and is in the following state:

- in Standby mode

- deselected

- Status Register values:

- ♦ The Write Enable Latch (WEL) bit is reset to 0.

- ♦ The Write In Progress (WIP) bit is reset to 0.

- ♦ The SRWD, BP1 and BP0 bits remain unchanged (non-volatile bits).

It is important to note that the device must not be accessed until  $V_{CC}$  reaches a valid and stable level within the specified [ $V_{CC}$  (min),  $V_{CC}$  (max)] range, as defined under Operating conditions.

#### 5.1.3 Power-up conditions

After powering on,  $V_{CC}$  will continuously increase from Vss to  $V_{CC}$ . During this time, the Chip Selection line (S #) does not allow to float, and the  $V_{CC}$  voltage must be followed. Therefore, it is recommended that the S-line be connected to  $V_{CC}$  by proper tensile strength.

In addition, the Chip Select (S#) input offers a built-in safety feature, as the S input is edge-sensitive as well as level-sensitive: after power-up, the device does not become selected until a falling edge has first been detected on Chip Select (S#). This ensures that Chip Select (S#) must have been high, prior to going low to start the first operation.

The  $V_{CC}$  voltage has to rise continuously from 0 V up to the minimum  $V_{CC}$  operating voltage defined under Operating conditions. After the Min.  $V_{CC}$  operation voltage, user has to wait 100us, then the chip can operation normally.

#### 5.1.4 Power-down

During power-down (continuous decrease of the  $V_{CC}$  supply voltage below the minimum  $V_{CC}$  operating voltage defined under Operating conditions), the device must be:

- deselected (Chip Select S# should be allowed to follow the voltage applied on Vcc),

- in Standby mode (there should not be any internal write cycle in progress).

## 5.2 Active Power and Standby Power modes

When Chip Select (S#) is low, the device is selected, and in the Active Power mode. The device consumes ICC.

When Chip Select (S#) is high, the device is deselected. If a Write cycle is not currently in progress, the device then goes into the Standby Power mode, and the device consumption drops to ICC1, as specified in DC characteristics.

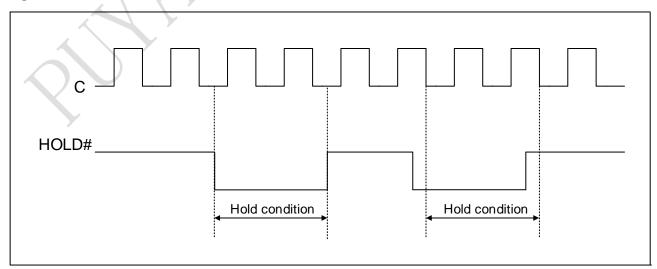

#### 5.3 Hold condition

HOLD# pin signal goes low to hold any serial communications with the device. The HOLD feature will not stop the operation of write status register, writing in progress.

The operation of HOLD requires Chip Select (S#) keeping low and starts on falling edge of HOLD# pin signal while Serial Clock (C) signal is being low (if Serial Clock signal is not being low, HOLD operation will not start until Serial Clock signal being low). The HOLD condition ends on the rising edge of HOLD# pin signal while Serial Clock (C) signal is being low (if Serial Clock signal is not being low, HOLD operation will not end until Serial Clock being low).

During the Hold condition, the Serial Data Output (Q) is high impedance, and the Serial Data Input (D) and the Serial Clock (C) are Don't Care.

Normally, the device is kept selected for the whole duration of the Hold condition. Deselecting the device while it is in the Hold condition has the effect of resetting the state of the device: this mechanism can be used, if required, to reset the ongoing processes [1] [2].

Figure 5-1 Hold condition activation

The Hold condition starts when the Hold (HOLD#) signal is driven low when Serial Clock (C) is already low (as shown in Figure 5-1).

Figure 5-1 also shows what happens if the rising and falling edges are not timed to coincide with Serial Clock (C) being low.

#### Note:

- 1. This resets the internal logic, except the WEL and WIP bits of the Status Register.

- 2. In the specific case where the device has moved in a Write command (Inst + Address + data bytes, each data byte being exactly 8 bits), deselecting the device also triggers the Write cycle of this decoded command.

## 5.4 Data protection and protocol control

The device has the following data protection mechanisms:

- Before accepting the execution of the Write and Write Status Register instructions, the device checks whether the number of clock pulses comprised in the instructions is a multiple of eight.

- The Write Enable Latch (WEL) bit indicates the status of the internal Write Enable Latch. When set to 1

the internal Write Enable Latch is set, when set to 0 the internal Write Enable Latch is reset and no Write

Status Register, write command is accepted.

- The Block Protect (BP1, BP0) bits in the Status Register are used to configure part of the memory as read-only.

- The Write Protect (W#) signal is used to protect the Block Protect (BP1, BP0) bits in the Status Register.

- For any instruction to be accepted, and executed, Chip Select (S#) must be driven high after the rising edge of Serial Clock (C) for the last bit of the instruction, and before the next rising edge of Serial Clock (C).

- Two points should be noted in the previous sentence:

- The "last bit of the instruction" can be the eighth bit of the instruction code, or the eighth bit of a data byte, depending on the instruction (except for Read Status Register (RDSR) and Read (READ) instructions).

- The "next rising edge of Serial Clock (C)" might (or might not) be the next bus transaction for some other device on the SPI bus.

Table 5-1 Write-protected block size

| BP1 | BP0 | Blocks        | Protected array addresses |

|-----|-----|---------------|---------------------------|

| 0   | 0   | None          | None                      |

| 0   | 1   | Upper quarter | C000h – FFFFh             |

| 1   | 0   | Upper half    | 8000h – FFFFh             |

| 1   | 1   | Whole memory  | 0000h – FFFFh             |

# 6. Instructions

Each command is composed of bytes (MSB bit transmitted first), initiated with the instruction byte, as summarized in Table 6-1.

If an invalid instruction is sent (one not contained in Table 6-1), the device automatically enters in a Wait state until deselected.

Table 6-1 Instruction set

| Instruction | Description                                     | Instruction format |

|-------------|-------------------------------------------------|--------------------|

| WREN        | Write Enable                                    | 0000 0110          |

| WRDI        | Write Disable                                   | 0000 0100          |

| RDSR        | Read Status Register                            | 0000 0101          |

| WRSR        | Write Status Register                           | 0000 0001          |

| READ        | Read from Memory Array                          | 0000 0011          |

| WRITE       | Write to Memory Array                           | 0000 0010          |

| RDID        | Read Identification Page                        | 1000 0011          |

| WRID        | Write Identification Page                       | 1000 0010          |

| RDLS        | Reads the Identification Page lock status       | 1000 0011          |

| LID         | Locks the Identification Page in read-only mode | 1000 0010          |

| RDUID       | Read UID number                                 | 1000 0011          |

For read and write commands to memory array and Identification Page the address is defined by two bytes as explained in Table 6-2.

Table 6-2 Significant bits within the address bytes (1) (2)

| Instruction   | Upper address byte |     |     |     |     |     |    | Lower address byte |    |    |    |    |    |    |    |    |

|---------------|--------------------|-----|-----|-----|-----|-----|----|--------------------|----|----|----|----|----|----|----|----|

| mstruction    | B15                | B14 | B13 | B12 | B11 | B10 | В9 | B8                 | B7 | B6 | B5 | B4 | В3 | B2 | B1 | В0 |

| READ or WRITE | A15                | A14 | A13 | A12 | A11 | A10 | A9 | A8                 | A7 | A6 | A5 | A4 | А3 | A2 | A1 | A0 |

| RDID or WRID  | х                  | Х   | х   | Х   | Х   | 0   | 0  | Х                  | Х  | A6 | A5 | A4 | А3 | A2 | A1 | A0 |

| RDLS or LID   | х                  | х   | х   | Х   | Х   | 1   | 0  | Х                  |    | Х  |    | Х  | Х  | Х  | Х  | Х  |

| RDUID         | х                  | х   | х   | Χ   | Х   | х   | 1  | Х                  | Х  | Х  | х  | Х  | А3 | A2 | A1 | A0 |

#### Note

- 1. A: Significant address bit

- 2. x: bit is Don't Care

#### 6.1 Write Enable (WREN)

The Write Enable (WREN) instruction is for setting Write Enable Latch (WEL) bit. For those instructions like WRITE.WRSR and WRID which are intended to change the device content, should be set every time after the WREN instruction setting the WEL bit.

As shown in Figure 6-1, the sequence of issuing WREN instruction is: S# goes low→ sending WREN instruction code→ S# goes high.

Figure 6-1 Write Enable (WREN) sequence

## 6.2 Write Disable (WRDI)

The Write Disable (WRDI) instruction is for resetting Write Enable Latch (WEL) bit.

As shown in Figure 6-2, the sequence of issuing WRDI instruction is: S# goes low→ sending WRDI instruction code→ S# goes high.

The Write Enable Latch (WEL) bit, in fact, becomes reset by any of the following events:

- Power-up

- WRDI instruction execution

- WRSR instruction completion

- WRID instruction completion

- WRITE instruction completion.

Figure 6-2 Write Disable (WRDI) sequence

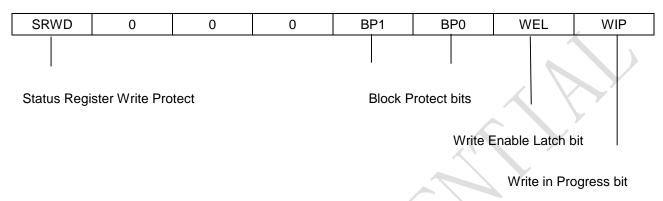

### 6.3 Read Status Register (RDSR)

The Read Status Register (RDSR) instruction is used to read the Status Register. The Status Register may be read at any time, even while a Write or Write Status Register cycle is in progress. When one of these cycles is in progress, it is recommended to check the Write in Progress (WIP) bit before sending a new instruction to the device. It is also possible to read the Status Register continuously, as shown in Figure 6-3.

Figure 6-3 Read Status Register (RDSR) sequence

#### 6.3.1 WIP bit

The Write in Progress (WIP) bit indicates whether the memory is busy with a Write or Write Status Register cycle. When set to 1, such a cycle is in progress, when reset to 0, no such cycle is in progress.

#### 6.3.2 WEL bit

When set to 1, the internal Write Enable Latch is set. When set to 0, the internal Write Enable Latch is reset, and no Write or Write Status Register instruction is accepted.

The WEL bit is returned to its reset state by the following events:

- Power-up

- Write Disable (WRDI) instruction completion

- Write Status Register (WRSR) instruction completion

- Write (WRITE) instruction completion

## 6.3.3 BP1, BP0 bits

The Block Protect (BP1, BP0) bits are nonvolatile. They define the size of the area to be software-protected against Write instructions. These bits are written with the Write Status Register (WRSR) instruction. When one or both of the Block Protect (BP1, BP0) bits is set to 1, the relevant memory area (as defined in Table 5-1) becomes protected against Write (WRITE) instructions. The Block Protect (BP1, BP0) bits can be written provided that the Hardware Protected mode has not been set.

#### 6.3.4 SRWD bit

The Status Register Write Disable (SRWD) bit is operated in conjunction with the Write Protect (W#) signal. The Status Register Write Disable (SRWD) bit and Write Protect (W#) signal enable the device to be put in the Hardware Protected mode (when the Status Register Write Disable (SRWD) bit is set to 1, and Write Protect (W#) is driven low). In this mode, the non-volatile bits of the Status Register (SRWD, BP1, BP0) become read-only bits and the Write Status Register (WRSR) instruction is no longer accepted for execution.

# 6.4 Write Status Register (WRSR)

The Write Status Register (WRSR) command allows new values to be written to the Status Register. Before it can be accepted, a Write Enable (WREN) command must previously have been executed. After the Write Enable (WREN) command has been decoded and executed, the device sets the Write Enable Latch (WEL).

The instruction sequence is shown in Figure 6-4. The sequence of issuing WRSR instruction is: S# goes low → sending WRSR instruction code → Status Register data on D→S# goes high.

Figure 6-4 Write Status Register (WRSR) sequence

Driving the Chip Select (S#) signal high at a byte boundary of the input data triggers the self-timed Write cycle

that takes tW to complete (as specified in AC tables in: DC and AC parameters).

While the Write Status Register cycle is in progress, the Status Register may still be read to check the value of the Write in progress (WIP) bit: the WIP bit is 1 during the self-timed Write cycle tW, and 0 when the Write cycle is complete. The WEL bit (Write Enable Latch) is also reset at the end of the Write cycle tW.

The Write Status Register (WRSR) instruction enables the user to change the values of the BP1, BP0 and SRWD bits:

- The Block Protect (BP1, BP0) bits define the size of the area that is to be treated as read-only, as defined in Table 5-1.

- The SRWD (Status Register Write Disable) bit, in accordance with the signal read on the Write Protect pin (W#), enables the user to set or reset the Write protection mode of the Status Register itself, as defined in Table 6-3. When in Write-protected mode, the Write Status Register (WRSR) instruction is not executed. The contents of the SRWD and BP1, BP0 bits are updated after the completion of the WRSR instruction, including the tW Write cycle. The Write Status Register (WRSR) instruction has no effect on the b6, b5, b4, b1, b0 bits in the Status Register. Bits b6, b5, b4 are always read as 0.

**Table 6-3 Protection modes**

| W# | SRWD bit | Mode                | Status register                                                  |  |  |  |

|----|----------|---------------------|------------------------------------------------------------------|--|--|--|

| 1  | 0        |                     | Statua ragistar ia writable                                      |  |  |  |

| 0  | 0        | Software-protected  | Status register is writable. the BP1 and BP0 bits can be changed |  |  |  |

| 1  | 1        |                     | the BFT and BFO bits can be changed                              |  |  |  |

| 0  | 1        | Hardware-protected  | Status Register is Hardware write-protected.                     |  |  |  |

| 0  | ı        | riaidware-protected | the BP1 and BP0 bits cannot be changed                           |  |  |  |

The protection features of the device are summarized in Table 6-3. When the state register write inhibit bit (SRWD) in the state register is 0 (its initial transfer state), the state register can be written (provided that the WEL bit has previously set by the WREN statement) and write-protected (W#) The logic level applied to the input pin is irrelevant.

When the Status Register Write Disable (SRWD) bit in the Status Register is set to 1, two cases should be considered, depending on the state of the Write Protect (W#) input pin:

- If Write Protect (W#) is driven high, it is possible to write to the Status Register (provided that the WEL bit has previously been set by a WREN instruction).

- If Write Protect (W#) is driven low, it is not possible to write to the Status Register even if the WEL bit has previously been set by a WREN instruction. (Attempts to write to the Status Register are rejected, and are not accepted for execution). As a consequence, all the data bytes in the memory area, which are Software-protected (SFP) by the Block Protect (BP1, BP0) bits in the Status Register, are also hardware-protected against data modification Regardless of the order of the two events.

- the Hardware-protected mode (HDP) can be entered by:

- either setting the SRWD bit after driving the Write Protect (W#) input pin low,

or driving the Write Protect (W#) input pin low after setting the SRWD bit.

Once the Hardware-protected mode (HDP) has been entered, the only way of exiting it is to pull high the Write Protect (W#) input pin.

If the Write Protect (W#) input pin is permanently tied high, the Hardware-protected mode (HDP) can never be activated, and only the Software-protected mode (SFP), using the Block Protect (BP1, BP0) bits in the Status Register, can be used.

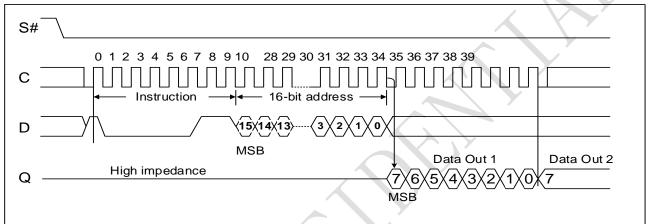

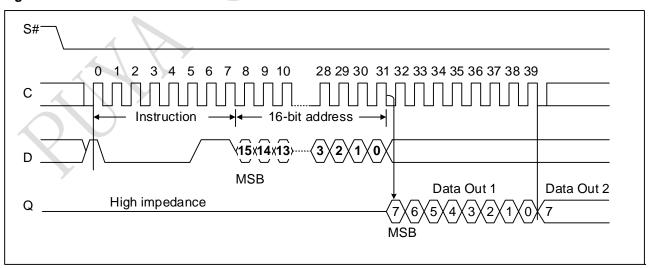

## 6.5 Read from Memory Array (READ)

The read instruction is for reading data out. The address is latched on rising edge of C, and data shifts out on the falling edge of C at a maximum frequency fR. The first address byte can be at any location. The address is automatically increased to the next higher address after each byte data is shifted out, so the whole memory can be read out at a single READ instruction. The address counter rolls over to 0 when the highest address has been reached.

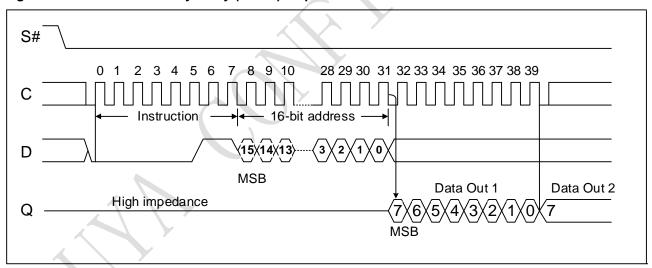

As shown in Figure 6-5, the sequence of issuing READ instruction is: S# goes low $\rightarrow$  sending READ instruction code $\rightarrow$  2-byte address on D $\rightarrow$  data out on Q $\rightarrow$  to end READ operation can use S# too high at any time during data out.

Figure 6-5 Read from Memory Array (READ) sequence

The instruction is not accepted, and is not executed, if a Write cycle is currently in progress.

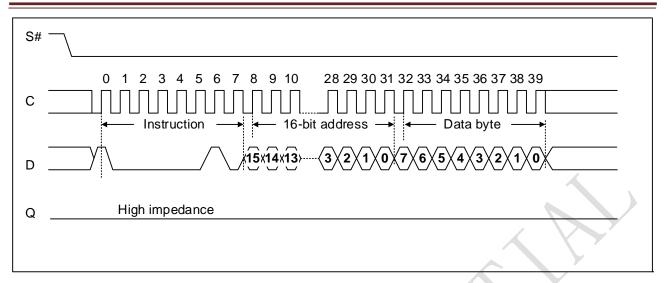

## 6.6 Write to Memory Array (WRITE)

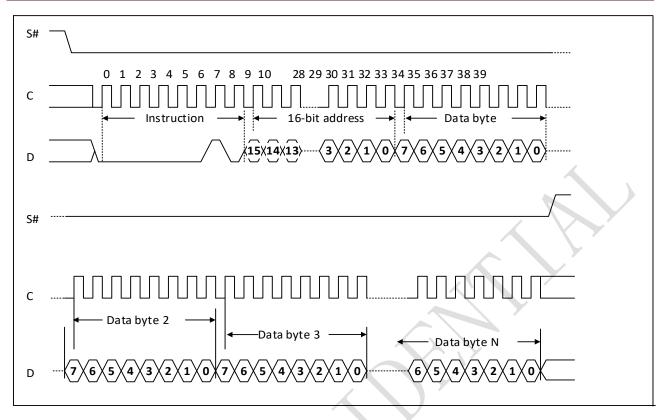

As shown in Figure 6-6, to send this instruction to the device, Chip Select (S#) is first driven low. The bits of the instruction byte, address byte, and at least one data byte are then shifted in, on Serial Data Input (D).

The instruction is terminated by driving Chip Select (S#) high at a byte boundary of the input data. The self-timed Write cycle, triggered by the Chip Select (S#) rising edge, continues for a period tW (as specified in AC characteristics in DC and AC parameters), at the end of which the Write in Progress (WIP) bit is reset to 0.

S#

0 1 2 3 4 5 6 7 8 9 10 28 29 30 31 32 33 34 35 36 37 38 39

C Instruction 16-bit address Data byte

D 15x14x13 32 10x7 6 5 4 3 2 1 0

Figure 6-6 Byte Write (WRITE) sequence

#### Note:

1. The self-timed write cycle tW is internally executed as a sequence of two consecutive events: [Erase addressed byte(s)], followed by [Program addressed byte(s)].

In the case of Figure 6-6, Chip Select (S#) is driven high after the eighth bit of the data byte has been latched in, indicating that the instruction is being used to write a single byte. However, if Chip Select (S#) continues to be driven low (as shown in Figure 6-7), the next byte of input data is shifted in, so that more than a single byte, starting from the given address towards the end of the same page, can be written in a single internal Write cycle.

Each time a new data byte is shifted in, the least significant bits of the internal address counter are incremented. If more bytes are sent than will fit up to the end of the page, a condition known as "roll-over" occurs. In case of roll-over, the bytes exceeding the page size are overwritten from location 0 of the same page.

The instruction is not accepted, and is not executed, under the following conditions:

- if the Write Enable Latch (WEL) bit has not been set to 1 (by executing a Write Enable instruction just before),

- if a Write cycle is already in progress,

- if the device has not been deselected, by driving high Chip Select (S#), at a byte boundary (after the eighth bit, b0, of the last data byte that has been latched in),

- if the addressed page is in the region protected by the Block Protect (BP1 and BP0) bits.

#### Figure 6-7 Page Write (WRITE) sequence

#### 6.6.1 Cycling with Error Correction Code (ECC)

P25C512H devices offer an Error Correction Code (ECC) logic. The ECC is an internal logic function transparent for the SPI communication protocol.

The ECC logic is implemented on each group of four EEPROM bytes[1]. Inside a group, if a single bit out of the four bytes happens to be erroneous during a Read operation, the ECC detects this bit and replaces it with the correct value. The read reliability is therefore much improved.

Even if the ECC function is performed on groups of four bytes, a single byte can be written/cycled independently. In this case, the ECC function also writes/cycles the three other bytes located in the same group[1]. As a consequence, the maximum cycling budget is defined at group level and the cycling can be distributed over the four bytes of the group: the sum of the cycles seen by byte0, byte1, byte2 and byte3 of the same group must remain below the maximum value.

Note: [1] A group of four bytes is located at addresses [4\*N, 4\*N+1, 4\*N+2, 4\*N+3], where N is an integer

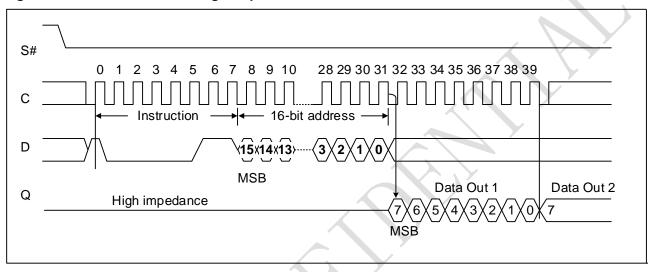

### 6.7 Read Identification Page (RDID)

The Identification Page (128 bytes) is an additional page that can be written and (later) permanently locked in Read-only mode.

Reading this page is achieved with the Read Identification Page instruction (see Table 6-1). The Chip Select signal (S#) is first driven low, the bits of the instruction byte and address bytes are then shifted in, on Serial Data Input (D). Address bit A10 must be 0, upper address bits are Don't Care, and the data byte pointed to by the lower address bits [A6~A0] is shifted out on Serial Data Output (Q). If Chip Select (S#) continues to be driven low, the internal address register is automatically incremented, and the byte of data at the new address is shifted out.

The number of bytes to read in the ID page must not exceed the page boundary, otherwise unexpected data is read (e.g.: when reading the ID page from location 20d, the number of bytes should be less than or equal to 108d, as the ID page boundary is 128 bytes).

The read cycle is terminated by driving Chip Select (S#) high. The rising edge of the Chip Select (S#) signal can occur at any time during the cycle. The first byte addressed can be any byte within any page.

The instruction is not accepted, and is not executed, if a write cycle is currently in progress.

Figure 6-8 Read Identification Page sequence

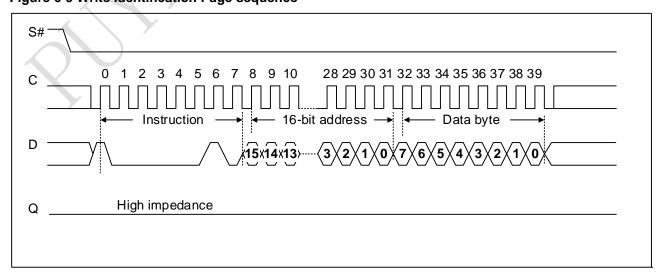

# 6.8 Write Identification Page (WRID)

The Identification Page (128 bytes) is an additional page that can be written and (later) permanently locked in Read-only mode.

Writing this page is achieved with the Write Identification Page instruction (see Table 6-1). The Chip Select signal (S#) is first driven low. The bits of the instruction byte, address bytes, and at least one data byte are then shifted in on Serial Data Input (D). Address bit A10 must be 0, upper address bits are Don't Care, the lower address bits [A6~A0] define the byte address within the Identification Page. The instruction sequence is shown in Figure 6-9.

Figure 6-9 Write Identification Page sequence

## 6.9 Read Lock Status (RDLS)

To determine if the identification page is locked in read-only mode, use the Read Lock Status instruction (see Table 6-1). The read lock status sequence is defined by the chip select (S #) being driven low first. Next, the bits of the instruction and address bytes are shifted into the serial data input (D). Address bit A10 must be 1. All other address bits are Don't Care. The Lock bit is the LSB (least significant bit) of the byte read on the Serial Data Output (Q). "1" when the lock is active, "0" when the lock is not active. If Chip Select (S #) is still driven low, the same data byte will be shifted out. Driving Chip Select (S #) high ends the read cycle.

The instruction sequence is shown in Figure 6-10.

Figure 6-10 Read Lock Status sequence

## 6.10 Lock ID (LID)

This instruction can be accepted, a Write Enable (WREN) instruction must have been executed.

Chip Select (S#) must be driven high after the rising edge of Serial Clock (C) that latches in the eighth bit of the data byte, and before the next rising edge of Serial Clock (C). Otherwise, the Lock ID instruction is not executed.

Driving Chip Select (S#) high at a byte boundary of the input data triggers the self-timed write cycle whose duration is tW (as specified in AC characteristics in: DC and AC parameters). The instruction sequence is shown in Figure 6-11.

The instruction is discarded, and is not executed, under the following conditions:

- If a Write cycle is already in progress,

- If the Block Protect bits (BP1,BP0) = (1,1),

- If a rising edge on Chip Select (S#) happens outside of a byte boundary.

Figure 6-11 Lock ID sequence

### 6.11 Read UID number (RDUID)

The UID number (16 bytes) is an additional page that can be Read-only.

Reading this page is achieved with the Read UID number instruction (see Table 6-1). The Chip Select signal (S#) is first driven low, the bits of the instruction byte and address bytes are then shifted in, on Serial Data Input (D). Address bit A9 must be 1, upper address bits are Don't Care, and the data byte pointed to by the lower address bits [A3~A0] is shifted out on Serial Data Output (Q). If Chip Select (S#) continues to be driven low, the internal address register is automatically incremented, and the byte of data at the new address is shifted out.

The read cycle is terminated by driving Chip Select (S#) high. The rising edge of the Chip Select (S#) signal can occur at any time during the cycle. The first byte addressed can be any byte within any page.

The instruction is not accepted, and is not executed, if a write cycle is currently in progress.

Figure 6-12 Read UID number

# 7. Power-up and delivery state

## 7.1 Power-up state

After power-up, the device is in the following state:

- Standby mode

- deselected (after power-up, wait 100us after V<sub>cc</sub> min voltage, a falling edge is required on Chip Select (S#) before any instructions can be started).

- not in the Hold condition

- the Write Enable Latch (WEL) is reset to 0

- Write in Progress (WIP) is reset to 0

The SRWD, BP1 and BP0 bits of the Status Register are unchanged from the previous power-down (they are non-volatile bits).

# 7.2 Initial delivery state

The device is delivered with the memory array and Identification Page bits set to all 1s (each byte = FFh).

The Status Register Write Disable (SRWD) and Block Protect (BP1 and BP0) bits are initialized to 0.

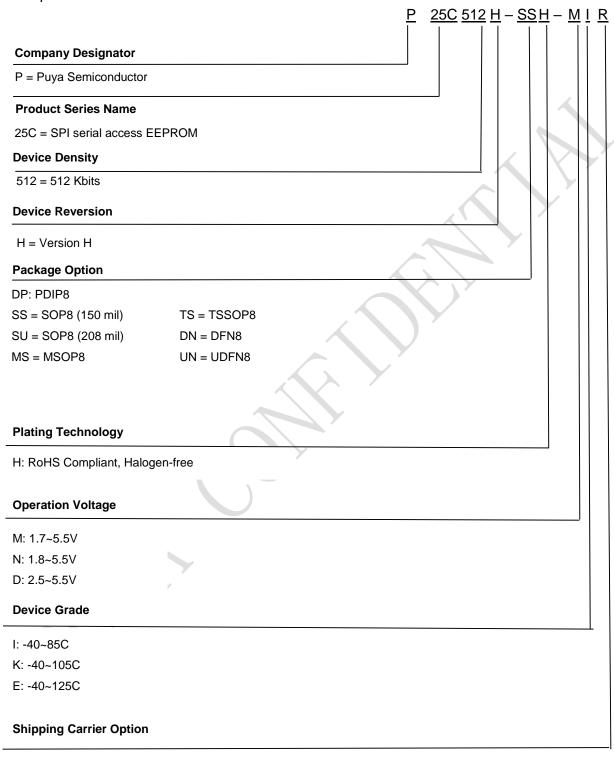

# 8. Ordering Code Detail

Example:

W: WAFER

T: TUBE

R: TAPE & REEL

# 9. Package information

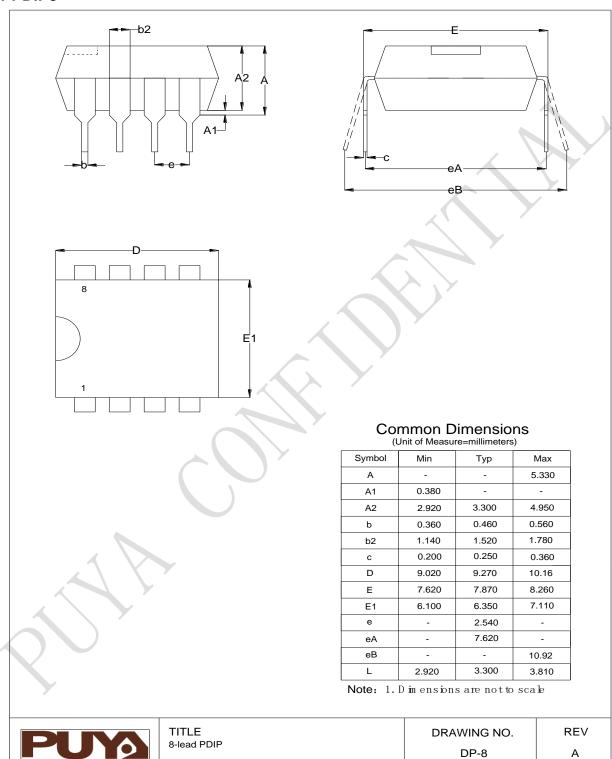

# 9.1 PDIP8

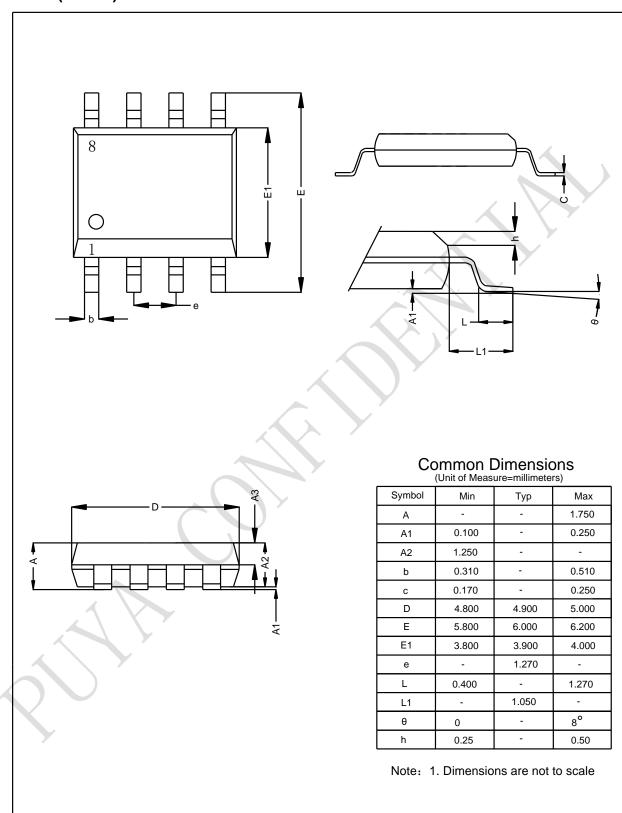

# 9.2 SOP8 (150mil)

Puya SOP8 (150mil) POD

TITLE

REV

1.0

DRAWING NO.

QRPD-0004

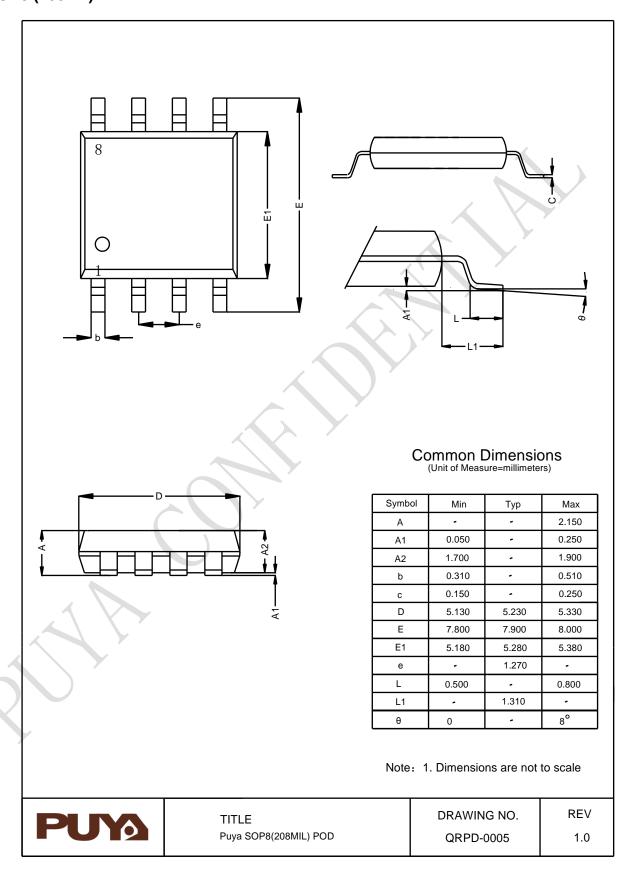

# 9.3 SOP8 (208mil)

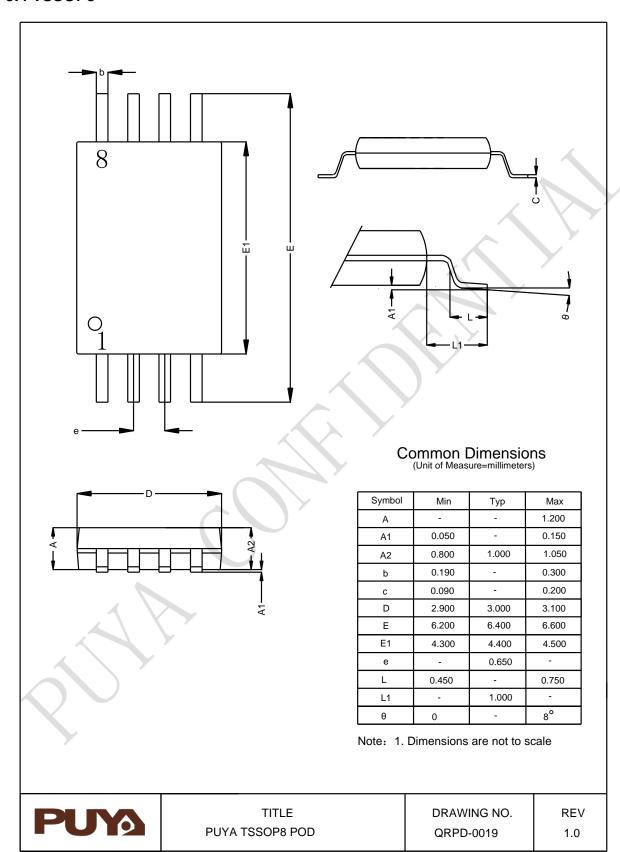

## **9.4 TSSOP8**

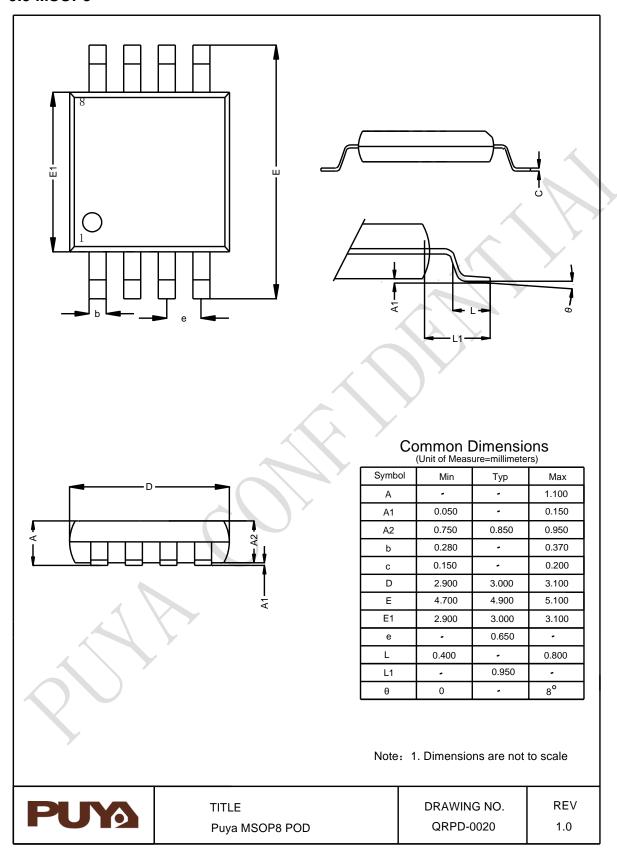

## 9.5 MSOP8

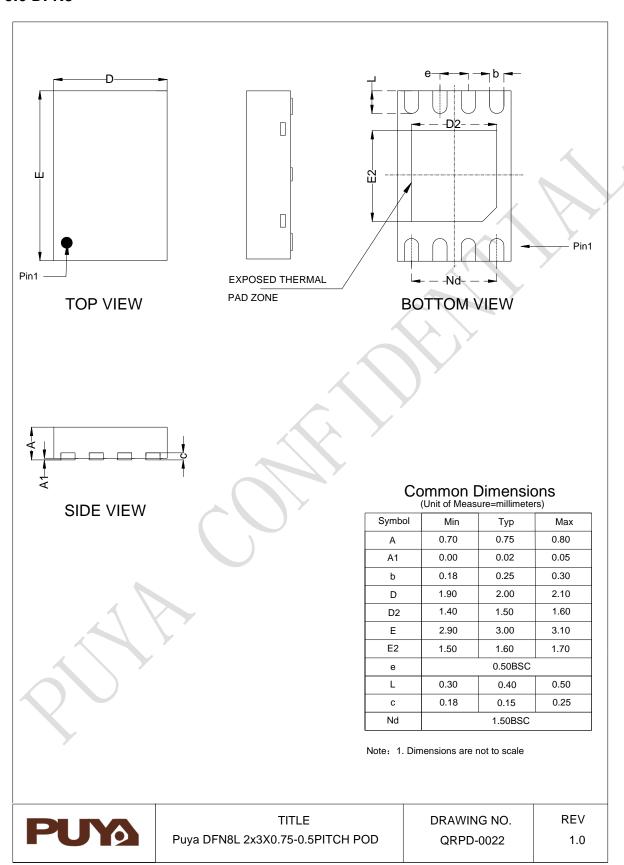

## 9.6 **DFN8**

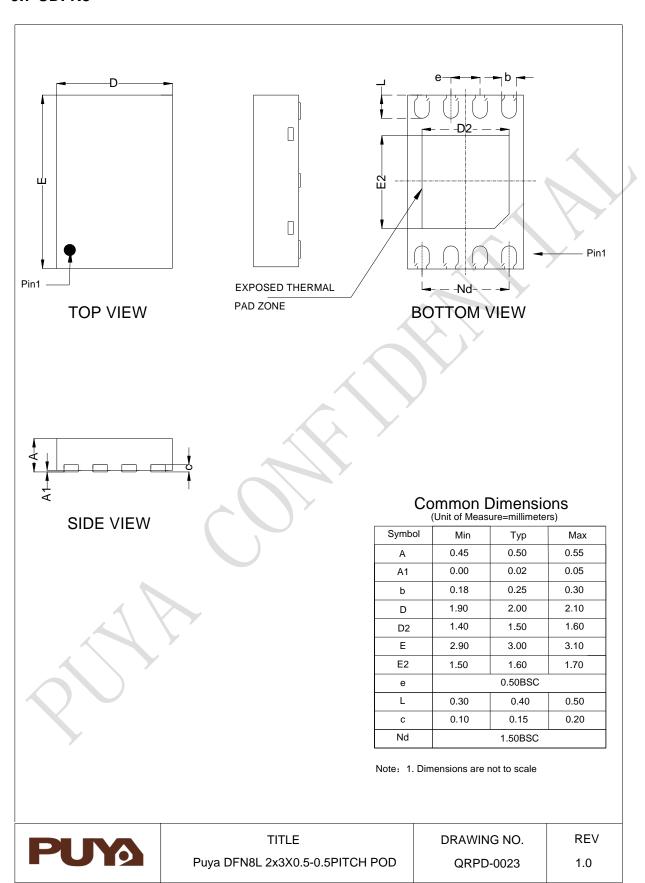

# 9.7 UDFN8

# 10. Revision History

| Version | Content                                       | Date       |  |

|---------|-----------------------------------------------|------------|--|

| Rev 1.0 | Initial Release                               | 2023-02-05 |  |

| Rev 1.1 | Update parameter of Isb,Icc1 and Icc2         | 2023-09-06 |  |

| Pov 1.2 | 1) Update parameter of ICC2                   | 2024-02-01 |  |

| Rev 1.2 | 2) Update Features and parameter in Table 4-5 |            |  |

|         |                                               | 4          |  |

Puya Semiconductor Co., Ltd.

#### **IMPORTANT NOTICE**

Puya Semiconductor reserves the right to make changes without further notice to any products or specifications herein. Puya Semiconductor does not assume any responsibility for use of any its products for any particular purpose, nor does Puya Semiconductor assume any liability arising out of the application or use of any its products or circuits. Puya Semiconductor does not convey any license under its patent rights or other rights nor the rights of others.